## ISL54405EVAL3Z Evaluation Board User Guide

## **Description**

The ISL54405EVAL3Z evaluation board is designed to provide a quick and easy method for evaluating the ISL54405 Stereo 2:1 Multiplexer IC.

The ISL54405 device is a unique IC. To use this evaluation board properly requires a thorough knowledge of the operation of the IC. Refer to the <a href="ISL54405">ISL54405</a> datasheet for an understanding of the functions and features of the device. Studying the device's truth table along with its pinout and block diagram on pages 1, 2 and 3 of the datasheet is the best way to get a quick understanding of how the part works.

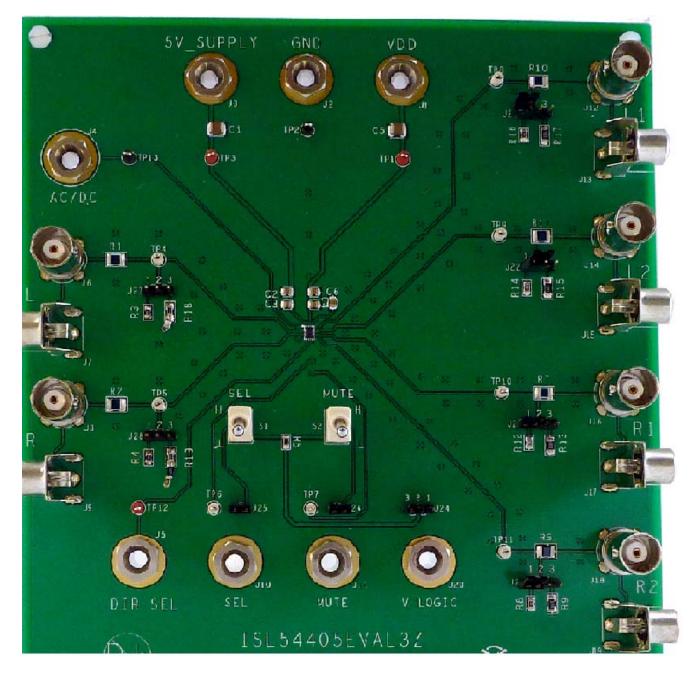

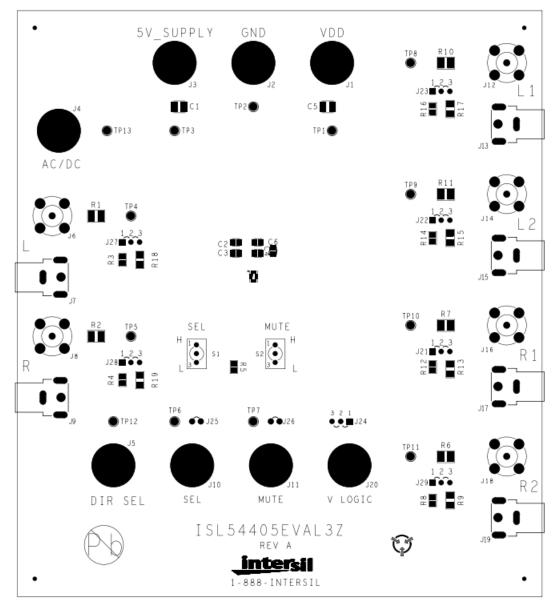

A picture of the main evaluation board is shown in Figure 4. The ISL54405 uTQFN IC is soldered onto the evaluation board. It is located in the center of the board and is designated as U1.

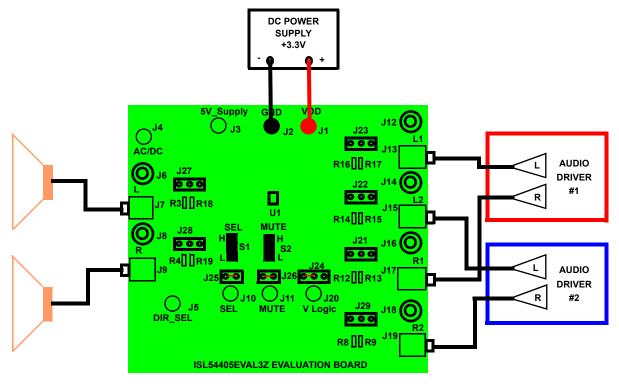

The ISL54405 IC is a single supply, bidirectional, dual single-pole/double-throw (SPDT) analog switch designed to function as a differential 2:1 multiplexer. It was designed for consumer and professional audio switching applications such as Computer Sound Cards and Home Theater products. It can be used to route a single stereo source to different line outs/loads (Figure 3) or to multiplex two stereo sources to a single load (Figure 1).

The part has various configurations of operation. The evaluation board contains standard jumpers, RCA connectors, BNC connectors, banana connectors, load resistors, and toggle

switches to allow the user to easily interface with the IC to evaluate its functions, features, and performance in the various modes of operation.

This application note will guide the user through the process of configuring and using the evaluation board to evaluate the ISL54405 device.

## **Key Features**

- RCA audio female jacks and BNC connectors

- Selectable  $32\Omega$  and  $20k\Omega$  resistor loads on the signal lines

- · Convenient test points and connections for test equipment

- Toggle switches for easy control of MUTE and SEL logic pins

- · Banana jacks for power, ground and logic control

## References

ISL54405 datasheet

TB494 Technical Brief "Intersil ISL54405 Hi-Fidelity Stereo 2:1 Multiplexer with Click and Pop Elimination"

## **Ordering Information**

| PART NUMBER    | DESCRIPTION               |  |

|----------------|---------------------------|--|

| ISL54405EVAL3Z | ISL54405 Evaluation Board |  |

FIGURE 1. ISL54405EVAL3Z MULTIPLEXING TWO STEREO SOURCES TO A SINGLE SPEAKER LOAD

## **Functional Description**

The ISL54405EVAL3Z Evaluation Board provides a simple platform to demonstrate the features and evaluate the performance of the ISL54405 IC. It provides easy access to the pins of the ISL54405 and convenient connectors/test points for connecting test equipment. The schematic, bill of materials and top silkscreen for the board are available on pages 8 through 10.

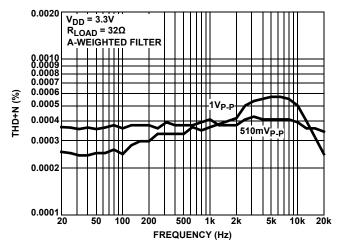

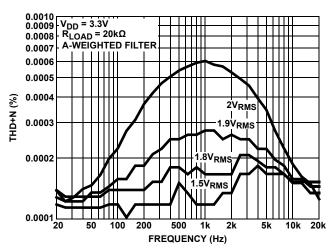

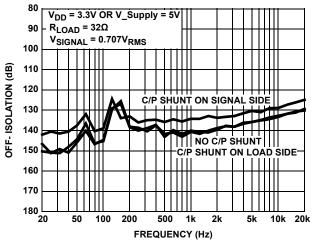

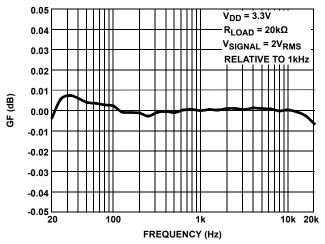

<u>Figures 6</u> through <u>13</u> show performance data taken using the evaluation board and an Audio Precision Dual Domain System Two Cascade Plus (SYS-2722) Generator/Analyzer. A video using this test equipment with the ISL54405 evaluation board is available at: <u>ISL54405 Video</u>.

The sections that follow will discuss using the evaluation board.

#### **Basic Layout of Evaluation Board**

The basic layout of the evaluation board is as follows: Refer to Figure 5 or the actual ISL54405EVAL3Z Rev A evaluation board.

Located in the center of the board is the ISL54405 IC (U1). The evaluation board has a pin 1 dot, to show how the IC should be oriented onto the evaluation board. The IC pin 1 indicator dot needs to be aligned with the evaluation board pin 1 dot indicator. The board comes with the IC soldered onto it.

Power for the IC is located at the top of the board through banana jacks J1 (VDD), J2 (GND), and J3 (5V\_SUPPLY). A DC voltage source must be connected between either VDD and GND or 5V\_SUPPLY and GND to power the part. For 3.3V operation, connect to the J1 (VDD) jack and leave J3 (5V\_SUPPLY) floating. For 5V operation, connect to the J3 (5V\_SUPPLY) jack and leave J1 (VDD) floating.

Access to the L and R COM side of the switch are through either the RCA female jacks J7 (L) and J9 (R) or BNC connectors J6 (L) and J8 (R) located on the left side of the board. The connectors J6 and J7 are connected in parallel and connectors J8 and J9 are connected in parallel.

Access to the L1, R1, L2, and R2 side of the switch is through either the RCA female jacks J13 (L1), J15 (L2), J17 (R1), and J19 (R2) or BNC connectors J12 (L1), J14 (L2), J16 (R1) and J18 (R2) located on the right side of the board. Note: The connectors J12 and J13 are connected in parallel, connectors J14 and J15 are connected in parallel, connectors J16 and J17 are connected in parallel, and connectors J18 and J19 are connected in parallel.

Logic control for the AC/DC and DIR\_SEL logic pins of the IC are through banana jacks J4 (AC/DC) and J5 (DIR\_SEL). Logic control for the SEL pin is through either the banana jack J10 (SEL) or the toggle switch S1 (SEL). Logic control of the MUTE pin is through either the banana jack J11 (MUTE) or the toggle switch S2 (MUTE).

For convenience, each of the COM I/O traces (L and R) and the signal pin I/O traces (L\_1, R\_1, L\_2, and R\_2) have selectable  $32\Omega$  or  $20k\Omega$  load resistors to ground. Either the  $32\Omega$  resistor or  $20k\Omega$  resistor can be connected to a trace by installing the appropriate jumper. No jumper would be installed if a resistor is not required as in the case when you would be connecting an actual speaker to the evaluation board. See the board schematic "ISL54405EVAL3Z Circuit Schematic" for the reference designators of the jumpers and resistors associated with each I/O.

In addition to the jumper selectable load resistors described in the previous paragraph, each of the traces also has a series resistor in each line (R1 at L, R2 at R, R6 at R2, R7 at R1, R10 at L1, and R11 at L2). These resistors come populated with a  $0\Omega$  resistor. These  $0\Omega$  resistors can be changed out with other value resistors or a capacitor if evaluating an AC coupled configuration.

### **Power Supply**

The ISL54405 IC requires either a 3.3V or 5V DC power supply for proper operation.

For 3.3V operation, the power supply is connected at banana jacks J1 (VDD) and J2 (GND). The power supply should be capable of delivering  $500\mu A$  of current. Nothing should be connected at banana jack J3 (5V\_SUPPLY).

For 5V operation, the power supply is connected at banana jacks J3 (5V\_SUPPLY) and J2 (GND). The power supply should be capable of delivering 500µA of current. Nothing should be connected at banana jack J1 (VDD).

## **Evaluation Board Logic Control**

The ISL54405 IC has four logic control pins; the AC/DC, DIR\_SEL, MUTE, and SEL. The MUTE and SEL control pins determine the state of the switches. The AC/DC and DIR\_SEL control pins determine the location of the ancillary  $40\Omega$  shunt resistors and if they are active or not. See the Truth Table on page 3 of the ISL54405 datasheet.

The ISL54405 logic is 1.8V CMOS compatible (Low  $\leq$  0.5V and High  $\geq$  1.4V) over a supply range of 3.0V to 3.6V at the VDD pin or 4.5V to 5.5V at the 5V\_SUPPLY pin. This allows control by a 1.8V or a 3V microcontroller.

Access to the AC/DC and DIR\_SEL pins are through banana jacks J4 (AC/DC) and J5 (DIR\_SEL) respectively. These pins should be driven HIGH or LOW by a microcontroller or permanently tied HIGH or LOW depending on the configuration and functionality that you are evaluating. The banana jacks allow the user to use standard Pomona banana plug cables to quickly connect these logic pins to ground or VDD to evaluate the various configurations of the ISL54405 part.

Access to the MUTE pin is through the banana jack J11 (MUTE) or the toggle switch S2 (MUTE). A jumper needs to be installed at jumper J26 to use the toggle switch.

Access to the SEL pin is through the banana jack J10 (SEL) or the toggle switch S1 (SEL). A jumper needs to be installed at jumper J25 to use the toggle switch.

The voltage connected at the high position (H) of the S1 and S2 toggle switches is determined by a jumper connected at jumper J24. To connect it to VDD, install a jumper at J24 position 2-3. To connect it to the J20 (VLOGIC) banana jack, install a jumper at J24 position 2-1. The VLOGIC jack is used whenever you want to use the toggle switches but have the control voltage at a different voltage than  $V_{DD}.$  For example,  $V_{DD}$  at 3.3V and VLOGIC high at 1.8V.

To control the MUTE and SEL from a microcontroller or external logic source you would remove the J25 and /or J26 jumpers and connected the logic controller at banana jacks J10 and/or J11.

Submit Document Feedback 2 intersil UG002.0 September 23, 2014

#### **SEL, MUTE CONTROL PINS**

The state of the ISL54405 device is determined by the voltage at the MUTE pin and the SEL pin. When MUTE is HIGH all channels of the ISL54405 multiplexer are OFF. When MUTE is LOW then the logic level at the SEL pin will determine which differential channels are ON. If SEL = LOW; L1/R1 are ON. If SEL = HIGH; L2/R2 are ON.

The MUTE has an internal pull-up resistor to the internal 3.3V supply rail and can be driven high or tri-stated (floated) by a microcontroller.

These pins are 1.8V logic compatible. When powering the part by the VDD pin, the logic voltage can be as high as the V<sub>DD</sub> voltage, which is typically 3.3V. When powering the part by the 5V\_SUPPLY pin, the logic voltage can be as high as the 5V\_SUPPLY voltage, which is typically 5V.

Logic Levels:

MUTE = Logic "0" (Low) when ≤ 0.5V

MUTE = Logic "1" (High) when ≥ 1.4V or floating

SEL = Logic "0" (Low) when ≤ 0.5V

SEL = Logic "1" (High) when ≥ 1.4V

#### AC/DC AND DIR\_SEL CONTROL PINS

The ISL54405 contains ancillary  $40\Omega$  shunt circuitry on its COM pins (L, R) and on its signal pins (L1, R1, L2, R2) that can be used for click/pop elimination in certain applications and used to get superior muting when connected to high impedance receiver loads  $(10k\Omega - 20k\Omega)$ .

The activation of this circuitry and whether it is located on the COM or signal side of the switch is determined by the logic levels applied at the AC/DC and DIR\_SEL pins. The DIR\_SEL control pin is only active when AC/DC is logic "1".

Note: An active shunt is only connected (ON) when the SPDT switch cell it is connected to is OFF. When in the MUTE state (MUTE = Logic "1") all activated shunts are ON.

When AC/DC is logic "0", all of the shunt circuitry on both sides of the switch are deactivated and not operable.

When AC/DC is logic "1", then the DIR\_SEL logic level determines whether the shunt circuitry will be activated on the COM side of the switch or on the signal side of the switch. When DIR\_SEL = Logic "1", the shunts on the COM side (L, R) are activated and inoperable on the signal side (L1, R1, L2, R2) of the switch. When DIR\_SEL = Logic "0" the shunts are activated on the signal side (L1, R1, L2, R2) and inoperable on the COM side (L, R).

Logic Levels:

AC/DC, DIR\_SEL = Logic "0" (Low) when ≤ 0.5V AC/DC, DIR\_SEL = Logic "1" (High) when ≥ 1.4V or floating.

The AC/DC and DIR\_SEL have internal pull-up resistors to the internal 3.3V supply rail and can be driven HIGH or tri-stated (floated) by the microcontroller. They should be driven to ground for a logic "0" (LOW). Note: For 5V applications the AC/DC and DIR\_SEL pins should never be driven to the external 5V rail. They need to be driven with 1.8V logic or 3V logic circuit.

## **Audio COM Pins (L and R)**

The evaluation board has two audio RCA female jacks labeled L (J7) and R (J9), which give you access to the COM pins of the ISL54405 IC. Each of these jacks have a BNC connector (J6 and J8, respectively) wired in parallel with the RCA jack.

The RCA jacks allow easy connection of a stereo speaker or a stereo audio source/generator. The BNC connectors allow easy connection of audio measurement and test equipment.

## Audio Signal Pins (L1, L2, R1, R2)

The evaluation board has RCA type connectors wired in parallel with BNC connectors which give access to the signal pins (L1, R1, L2, R2) of the IC.

You can connect an audio source/generator or speaker/amplifier load at these connectors. For example, Figure 1 shows two stereo sources connected at the signal pins (audio source 1 connected at L1 and R1; audio source 2 connected at L2 and R2). A stereo speaker set is connected at the COM pins (L and R). In this application the ISL54405 is used to multiplex two stereo audio sources to a single stereo speaker load.

## **Applications**

The ISL54405 was designed primarily for consumer and professional audio switching applications such as computer sound cards and home theater products. In a typical sound card application the ISL54405 is used for the following applications:

- To route a single stereo source to either the front or back line outs of the computer sound card.

- To multiplex two stereo sources to a single line out of the computer sound card.

#### **Test Points**

The board has various test points for ease of connecting probes to make measurements. The test points available are described in Table 1.

TABLE 1.

| DESIGNATOR | DESCRIPTION                    |  |

|------------|--------------------------------|--|

| TP1        | VDD test point                 |  |

| TP2        | Ground test point              |  |

| TP3        | 5V_SUPPLY test point           |  |

| TP4        | L test point                   |  |

| TP5        | R test point                   |  |

| TP6        | SEL logic input test point     |  |

| TP7        | MUTE logic input test point    |  |

| TP8        | L1 test point                  |  |

| TP9        | L2 test point                  |  |

| TP10       | R1 test point                  |  |

| TP11       | R2 test point                  |  |

| TP12       | DIR_SEL logic input test point |  |

| TP13       | AC/DC logic input test point   |  |

## **User Guide 002**

## **Board Component Definitions**

| DESIGNATOR | DESCRIPTION                                                                         |  |  |

|------------|-------------------------------------------------------------------------------------|--|--|

| U1         | ISL54405 uTQFN IC                                                                   |  |  |

| J1         | VDD power supply connection (3.3V <sub>DC</sub> )                                   |  |  |

| J2         | Ground connection                                                                   |  |  |

| 13         | 5V_SUPPLY power supply connection (5V <sub>DC</sub> )                               |  |  |

| J4         | AC/DC logic input                                                                   |  |  |

| J5         | DIR_SEL logic input                                                                 |  |  |

| J6, J7     | L common side I/O                                                                   |  |  |

| J8, J9     | R common side I/O                                                                   |  |  |

| J10        | SEL logic input                                                                     |  |  |

| J11        | MUTE logic input                                                                    |  |  |

| J12, J13   | L1 signal side I/O                                                                  |  |  |

| J14, J15   | L2 signal side I/O                                                                  |  |  |

| J16, J17   | R1 signal side I/O                                                                  |  |  |

| J18, J19   | R2 signal side I/O                                                                  |  |  |

| J20        | External logic DC voltage for MUTE and SEL                                          |  |  |

| J21        | Load jumper for R1 (Position 1-2 for $20k\Omega$ , Position 2-3 for $32\Omega$ )    |  |  |

| J22        | Load jumper for L2 (Position 1-2 for $20k\Omega$ , Position 2-3 for $32\Omega$ )    |  |  |

| J23        | Load jumper for L1 (Position 1-2 for 20kΩ, Position 2-3 for 32Ω)                    |  |  |

| J27        | Load jumper for L COM (Position 1-2 for $20k\Omega$ , Position 2-3 for $32\Omega$ ) |  |  |

| J28        | Load jumper for R COM (Position 1-2 for 20kΩ, Position 2-3 for 32Ω)                 |  |  |

| J29        | Load jumper for R2 (Position 1-2 for $20k\Omega$ , Position 2-3 for $32\Omega$ )    |  |  |

| J24        | S1 and S2 voltage jumper, (Position 1-2 voltage at J20, Position 2-3 connect to VDD |  |  |

| J25        | SEL jumper (install jumper to use S1 switch)                                        |  |  |

| J26        | MUTE jumper (install jumper to use S2 switch)                                       |  |  |

| <b>S1</b>  | SEL switch                                                                          |  |  |

| <b>S</b> 2 | MUTE switch                                                                         |  |  |

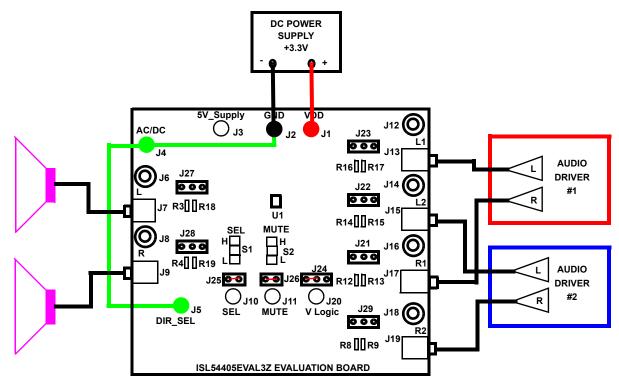

FIGURE 2. BASIC EVALUATION TEST SETUP BLOCK DIAGRAM (Multiplexing Two Stereo Sources to One Speaker)

## Using the Board to Multiplex Between Two Audio Sources

Refer to Figure 2.

#### Lab Equipment

The equipment, external supplies and signal sources needed to operate the board are:

- 1. 3.3V DC power supply.

- 2. Two stereo audio sources or audio signal generators.

- 3. Set of stereo speakers or use on board resistor loads.

## **Initial Board Setup Procedure**

- Attach the main evaluation board to the DC power supply at J1 (V<sub>DD</sub>) and J2 (GND). Positive terminal at J1 and negative terminal at J2. The supply should be capable of delivering 3.0V to 5V and 1mA of current. Set the supply voltage to 3.3V.

- Configure the board to use the S1 (SEL) and S2 (MUTE) toggle switches by installing jumpers at J25, J26 and J24 at location 2-3. In this configuration, when a toggle switch is in L position, the logic pin will be driven to ground. When its in the H position, the logic pin will be driven to the VDD voltage of 3.3V.

- 3. Disable all ancillary 40  $\!\Omega$  shunt resistors by connecting J4 (AC/DC) and J5 (DIR\_SEL) to J2 (GND).

- 4. Put the S2 (MUTE) toggle switch in the "H" position. This will put the IC into the mute state.

- 5. Put the S1 (SEL) toggle switch in the "L" position.

- Connect the audio source 1 left channel to the J13 (L1) RCA connector or the J12 (L1) BNC connector and the right

- channel to the J17 (R1) RCA connector or J16 (R1) BNC connector.

- Connect the audio source 2 left channel to the J15 (L2) RCA connector or the J14 (L2) BNC connector and the right channel to the J19 (R2) RCA connector or J18 (R2) BNC connector.

- Connect one speaker to the J7 (L) RCA connector or the J6 (L) BNC connector and the other speaker to the J9 (R) RCA connector or J8 (R) BNC connector.

#### **Audio Mute and Playback Operation**

- Verify that the toggle switch S2 (MUTE) is in the "H" position. All switches will be off.

- 2. Turn audio driver #1 on.

- 3. Turn audio driver #2 on.

- 4. Put the S1 (SEL) toggle switch in the "L" position.

- 5. Take the S2 (MUTE) toggle switch to the "L" position.

- The audio signal from driver #1 should be heard in the speakers.

- Take the S2 (MUTE) toggle switch to the "H" position. Audio sources will be muted.

- 8. Put the S1 (SEL) toggle switch in the "H" position.

- 9. Take the S2 (MUTE) toggle switch to the "L" position.

- The audio signal from driver #2 should be heard in the speakers.

- 11. Toggle the S1 (SEL) switch to the "L" position to play source #1. Toggle it back to the "H" position to play source #2.

Submit Document Feedback 5 Intersil UG002.0

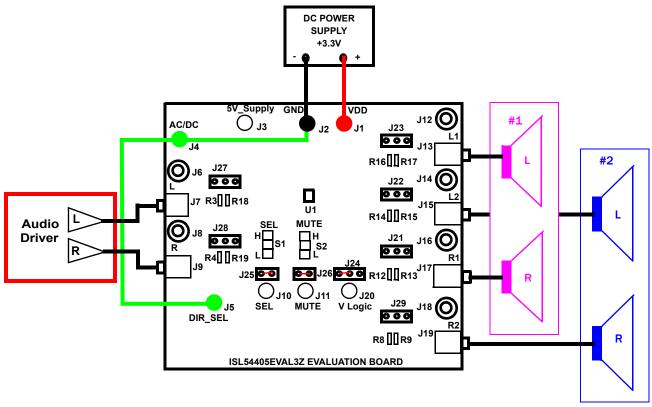

FIGURE 3. BASIC EVALUATION TEST SETUP BLOCK DIAGRAM (Multiplex One Stereo Source to Two Stereo Speakers)

# Using the Board to Multiplex Between Two Stereo Speakers

Refer to Figure 3.

#### Lab Equipment

The equipment, external supplies and signal sources needed to operate the board are listed below:

- 1. 3.3V DC power supply.

- 2. Stereo Audio source or audio signal generator.

- 3. Two sets of stereo speakers or use on board resistor loads.

#### **Initial Board Setup Procedure**

- Attach the main evaluation board to the DC power supply at J1 (V<sub>DD</sub>) and J2 (GND). Positive terminal at J1 and negative terminal at J2. The supply should be capable of delivering 3.0V to 5V and 1mA of current. Set the supply voltage to 3.3V.

- Configure the board to use the S1 (SEL) and S2 (MUTE) toggle switches by installing jumpers at J25, J26 and J24 at location 2-3. In this configuration, when a toggle switch is in L position, the logic pin will be driven to ground. When its in the H position, the logic pin will be driven to the VDD voltage of 3.3V.

- Disable all ancillary 40Ω shunt resistors by connecting J4 (AC/DC) and J5 (DIR\_SEL) to J2 (GND).

- 4. Put the S2 (MUTE) toggle switch in the "H" position. This will put the IC in to the mute state.

- 5. Put the S1 (SEL) toggle switch in the "L" position.

- Connect the audio source left channel to the J7 (L) RCA connector or the J6 (L) BNC connector and the right channel to the J9 (R) RCA connector or J8 (R) BNC connector.

- Connect one stereo speaker to the J13 (L1) RCA connector or the J12 (L1) BNC connector and the right channel to the J17 (R1) RCA connector or J16 (R1) BNC connector.

- Connect the other stereo speaker to the J15 (L2) RCA connector or the J14(L2) BNC connector and the other speaker to the J19 (R2) RCA connector or J18 (R2) BNC connector.

#### **Audio Mute and Playback Operation**

- Verify that the toggle switch S2 (MUTE) is in the "H" position. All switches will be off.

- 2. Turn the audio driver on.

- 3. Put the S1 (SEL) toggle switch in the "L" position.

- 4. Take the S2 (MUTE) toggle switch to the "L" position.

- The audio signal from driver should be heard in the speaker connected at L1 and R1.

- Take the S2 (MUTE) toggle switch to the "H" position. Audio source will be muted.

- 7. Put the S1 (SEL) toggle switch in the "H" position.

- 8. Take the S2 (MUTE) toggle switch to the "L" position.

- The audio signal from driver should be heard in the speaker connected at L2 and R2.

- Toggle the S1 (SEL) switch to route the audio signal between the two stereo speakers.

Submit Document Feedback 6 Intersil UG002.0

# **ISL54405EVAL3Z Evaluation Board**

FIGURE 4. TOP SIDE

**ISL54405EVAL3Z Circuit Schematic**

тр6

J25

J11 MUTE 🖼

J10

SEL 🕥

S1 H

SEL 7L

↓ R2

#### VDD DIR\_SEL 5V\_SU PPLY GND AC/DC **J**4 J2 ۵ J1 J5 🖺 R10 VDD J12 C5 C1 10µF C2 10μF TP12 () C6 0.1µF 0.1μF C3 <u>C</u>7 **⊕**TP1 трз 🔘 0.01µF 0.01µF TP4 **⊕TP2** R1 C4 ) J14 0.1µF J27 R11 16 15 14 13 **⊕** TP8 фa 12 U1 11 10 - ТР9 UT QFN16 **₽** J16 **→** TP10 R2 R7 5 6 7 8 J28 VDD V LOGIC R6 J18 J24 J29 J21 J22 J23 J9 🌲

R15 32.4

← TP7

J26

S2 H

MUTE

## **User Guide 002**

# ISL54405EVAL3Z Bill of Materials (Revision A)

| QTY | UNITS | REFERENCE<br>DESIGNATOR       | DESCRIPTION                                                | MFR                   | MANUFACTURER'S<br>PART NUMBER |

|-----|-------|-------------------------------|------------------------------------------------------------|-----------------------|-------------------------------|

| 1   | ea    |                               | PWB-PCB, ISL54405EVAL3Z, Rev A, uTQFN, ROHS                | IMAGINEERING<br>INC   | ISL54405EVAL3ZREVAPCB         |

| 2   | ea    | C3, C7                        | CAP, SMD, 0805, 0.01µF, 50V, 10%, X7R, R0HS                | KEMET                 | C0805C103K5RACTU              |

| 3   | ea    | C2, C4, C6                    | CAP, SMD, 0805, 0.1μF, 50V, 10%, X7R, R0HS                 | KEMET                 | C0805C104K5RACTU              |

| 2   | ea    | C1, C5                        | CAP, SMD, 1210, 10µF, 25V, 10%, X7R, ROHS                  | AVX                   | 12103C106KAT2A                |

| 8   | ea    | J1-J5, J10, J11, J20          | CONN - JACK, BANANA - SS - SDRLESS, VERTICAL, ROHS         | JOHNSON<br>COMPONENTS | 108-0740-001                  |

| 6   | ea    | J6, J8, J12, J14, J16,<br>J18 | CONN - BNC, RECEPTACLE, TH, 4 POST, 50Ω, GOLDCONTACT, ROHS | AMPHENOL              | 31-5329-52RFX                 |

| 3   | ea    | TP1, TP3, TP12                | CONN-MINI TEST PT, VERTICAL, RED, ROHS                     | KEYSTONE              | 5000                          |

| 2   | ea    | TP2, TP13                     | CONN-MINI TEST PT, VERTICAL, BLK, ROHS                     | KEYSTONE              | 5001                          |

| 8   | ea    | TP4-TP11                      | CONN-MINI TEST PT, VERTICAL, WHITE, ROHS                   | KEYSTONE              | 5002                          |

| 7   | ea    | J21-J24, J27-J29              | CONN-HEADER, 1X3, BREAKAWY 1X36, 2.54mm, ROHS              | BERG/FCI              | 68000-236HFL                  |

| 2   | ea    | J25, J26                      | CONN-HEADER, 1X2, RETENTIVE, 2.54mm, 0.230X0.120, ROHS     | BERG/FCI              | 69190-202HLF                  |

| 6   | ea    | J7, J9, J13, J15, J17,<br>J19 | CONN-RCA PHONO JACK, WHITE, 3.6mm, R/A, ROHS, PCB MNT      | CUI, INC              | RCJ-013                       |

| 1   | ea    | U1                            | ic-DUAL, SPDT ANALOG SWITCH, 16P, uTQFN, 2.6X1.8, ROHS     | INTERSIL              | ISL54405IRUZ                  |

| 1   | ea    | R5                            | RES, SMD, 0805, $0\Omega$ , 1/8W, TF, ROHS                 | YAGEO                 | RC0805JR-070RL                |

| 6   | ea    | R3, R4, R8, R12,<br>R14, R16  | RES, SMD, 0805, 20k, 1/8W, 1%, TF, ROHS                    | VENKEL                | CR0805-8W-2002FT              |

| 6   | ea    | R9, R13, R15, R17-<br>R19     | RES, SMD, 1206, 32.4 $\Omega$ , 1/4W, 1%, TF, ROHS         | YAGEO                 | RC1206FR-0732R4L              |

| 6   | ea    | R1, R2, R6, R7, R10,<br>R11   | RES, SMD, 1210, $0\Omega$ , 1/4W, TF, ROHS                 | VENKEL                | CR1210-4W-000                 |

| 4   | ea    | Four Corners                  | SCREW, 4-40X1/4in, PAN, SS, PHILLIPS                       |                       |                               |

| 4   | ea    | Four Corners                  | STANDOFF, 4-40X3/4in, F/F, HEX, ALUMINUM, ROHS             | KEYSTONE              | 2204 (.250 OD)                |

| 1   | ea    | Place assy in bag             | BAG, STATIC, 1 0X12, ZIP LOC                               | INTERSIL              | 212403-015                    |

| 2   | ea    | S1, S2                        | SWITCH-MINI TOGGLE, TH, SPDT, 0.4VA, ON-OFF-ON, ROHS, GOLD | C&K<br>COMPONENTS     | ET03SD1CBE                    |

| 1   | ea    | AFFIX TO BACK OF PCB          | LABEL-DATE CODE_LINE 1: YRWK/REV#, LINE 2: BOM NAME        | INTERSIL              | LABEL-DATE CODE               |

## **Board Silk Screen**

FIGURE 5. TOP LAYER SILK SCREEN

# **Typical Performance Curves** Unless noted: $V_{IN}$ = 12V, $V_{OUT}$ = 3.3V, $f_{SW}$ = 400kHz, $T_A$ = +25°C

FIGURE 6. THD+N vs SIGNAL LEVELS vs FREQUENCY

FIGURE 7. THD+N vs SIGNAL LEVELS vs FREQUENCY

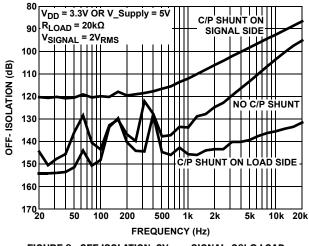

FIGURE 8. OFF-ISOLATION,  $0.707V_{\mbox{RMS}}$  SIGNAL,  $32\Omega$  LOAD

FIGURE 9. OFF-ISOLATION,  $2V_{\mbox{RMS}}$  SIGNAL,  $20k\Omega$  LOAD

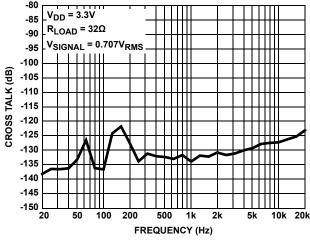

FIGURE 10. CHANNEL-TO-CHANNEL CROSSTALK

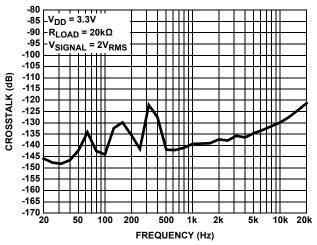

FIGURE 11. CHANNEL-TO-CHANNEL CROSSTALK

## Typical Performance Curves Unless noted: V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 3.3V, f<sub>SW</sub> = 400kHz, T<sub>A</sub> = +25 °C (Continued)

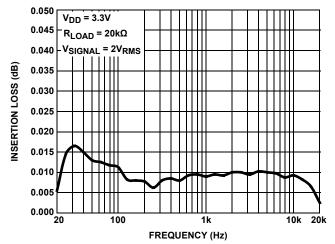

FIGURE 12. INSERTION LOSS vs FREQUENCY

FIGURE 13. GAIN vs FREQUENCY

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.